最近,彭博社的一篇“小作文”又给国内公司带来了很大困扰。在文章中,他们谈到,这家国内公司将发力SAQP 技术,以绕过某些限制。按照彭博说的说法,SAQP技术能够让企业在没有EUV光刻机的情况下,生产更先进的芯片。

那么,什么是SAQP?这是self-aligned quadruple patterning的简称,也就是自对准四重图案化。在介绍SAQP之前,我们先要了解一下什么是多图案技术。

多图案化技术

多重图案化是一种克服芯片制造过程中光刻限制的技术。如今的单次曝光、193nm 波长光刻在 40nm 半节距处达到了物理极限。多重图案化使芯片制造商能够对 20 纳米及以下的 IC 设计进行成像。

基本上,多重图案有两个主要类别:间距分割(pitch splitting)和间隔物(spacer)。建个份额是一个总括术语,包括双重图案化(double patterning)和三重图案化(triple patterning)技术。同时,间隔物包括自对准双重图案化(SADP:self-aligned quadruple patterning )和自对准四重图案化(SAQP)。间隔分割和间隔技术都可以扩展到八联体图案(octuplet patterning)。

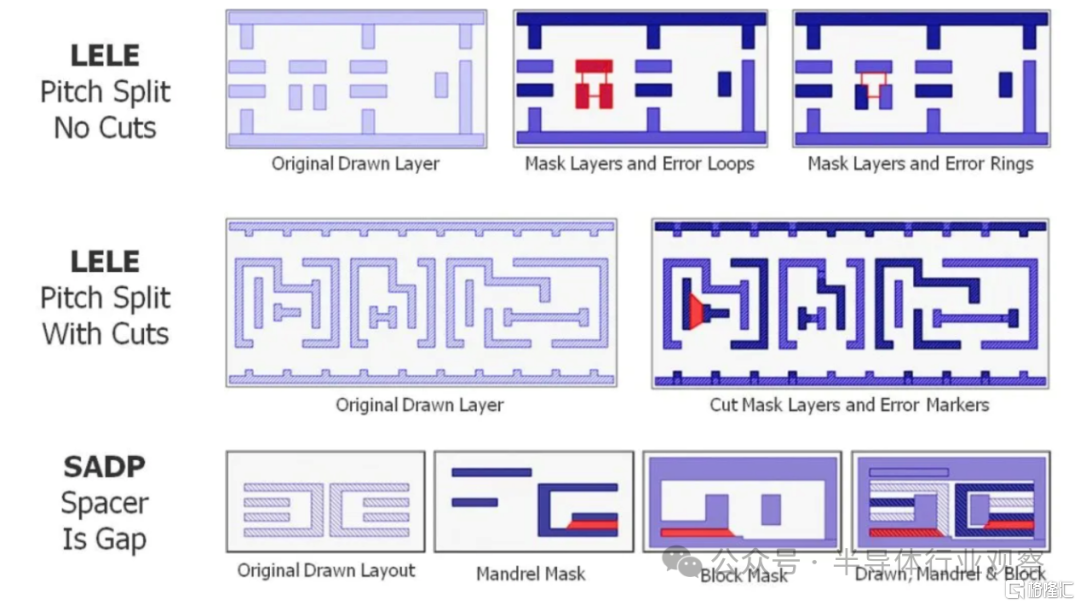

第一种类型,间距分割,主要用于逻辑中。最常见的间距分割形式是双重图案化。在设计方面,双重图案化几乎总是指光刻-蚀刻-光刻-蚀刻 (LELE:litho-etch-litho-etch-litho-etch) 间距分割工艺。在晶圆厂中,LELE 需要两个独立的光刻和蚀刻步骤来定义单个层。据 Sematech 称,LELE 可将pitch降低 30%。但 LELE 可能很昂贵,因为它使光刻流程中的工艺步骤加倍。

最初,该技术将无法通过单次曝光印刷的布局分开,形成两个较低密度的掩模。然后,它使用两个单独的曝光过程。这又形成了两个较粗糙的图案。它们被组合和叠加,从而能够在晶圆上形成更精细的图像。

LELE(即双重图案化:double patterning)对设计人员提出了新的布局、物理验证和调试要求。例如,在设计方面,根据间距要求为掩模层分配颜色。遮罩层从原始绘制的布局分割或分解为两个新层。

一个关键的方法决策与是否希望设计师看到一个统称为““colorless”设计流程。另一种选择是双色(two-color)流程,其中设计者贴出两个掩模,选择几个分解选项之一。当然,任何设计流程都需要权衡。

在 20 纳米,代工厂正在使用几种不同的双图案设计流程。更常见的流程之一实际上并不要求设计团队将其图层分解为两种颜色。然而,在某些情况下,设计者可能想知道颜色分配是什么。尽管这听起来很合理,但看到双重图案颜色很可能会降低调试效率。

与此同时,在 10nm 节点,芯片制造商可能需要转向另一种节距分割技术——三重图案化。三重图案化的一种形式是光刻-蚀刻-光刻-蚀刻-光刻-蚀刻(LELELE)。LELELE与LELE类似。在晶圆厂中,LELELE 需要三个独立的光刻和蚀刻步骤来定义单个层。

在设计方面,三重图案化需要将原始层分解为三个掩模。三个掩模的形状在制造过程中结合起来形成最终的形状。三重图案从外面看起来可能无害,但潜在的混乱就在里面。构建 EDA 软件算法来使用三重图案自动分解、着色和检查层是一项挑战。三重图案违规可能非常复杂,并且调试可能很困难。

同时,间隔物是多重图案化的第二个主要类别。它也称为 SADP 和 SAQP。SADP/SAQP 曾用于将 NAND 闪存扩展到 1xnm 节点,现在正在进入逻辑领域。

SADP 是双重图案化的一种形式。它有时被称为节距分割(pitch division)或侧壁辅助双图案化(sidewall-assisted double patterning)。SADP 工艺使用一个光刻步骤以及额外的沉积和蚀刻步骤来定义类似间隔物的特征。在SADP工艺中,第一步是在基板上形成心轴。(mandrels)然后,用沉积层覆盖该图案。然后蚀刻沉积层,从而形成间隔物。最后,顶部部分经历化学机械抛光(CMP)步骤。

SAQP 基本上是侧壁间隔物双图案化技术的两个周期。简单的图案,包括闪存中的图案或 finFET 中的鳍片,都是在 SADP 或 SAQP 中完成的。在这种技术中,先形成单独的平行线,然后进行切割。同时,DRAM和逻辑芯片中的金属层更加复杂,无法通过SADP/SAQP来完成。这些金属层需要LELE。SADP/SAQP 的设计灵活性也低于 LELE,而 LELE 型技术需要孔型图案。

SAQP又是什么?

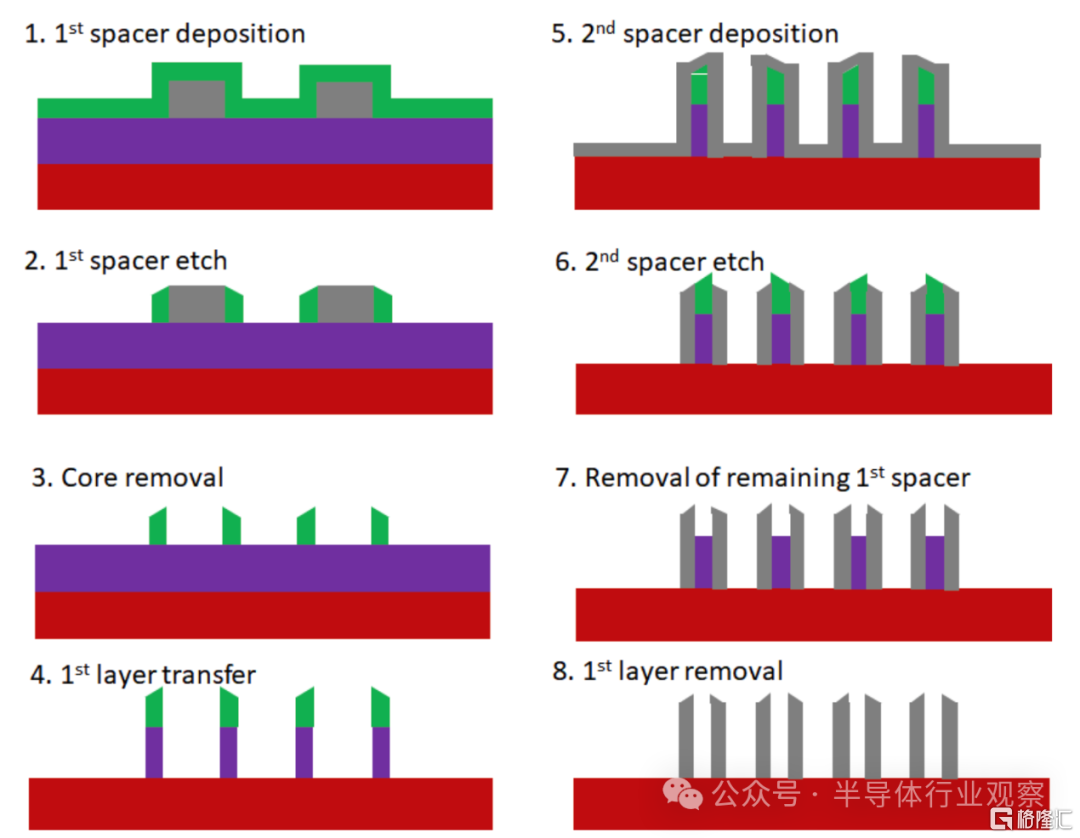

相关资料显示,自对准四重图案化 (SAQP) 是用于对小于 38 nm 的特征节距进行图案化的最广泛使用的技术,预计能够达到 19 nm 节距。它实际上是多个工艺步骤的集成,已用于 FinFET和 1X DRAM的鳍片图案化。这些步骤如图 1 所示,允许最初绘制的相距 80 nm 的线生成最终相距 20 nm 的线(实际上是 10 nm 分辨率)。这很重要,因为它远远超出了任何大批量光刻工具的分辨率,包括 EUV(13 nm 分辨率)。

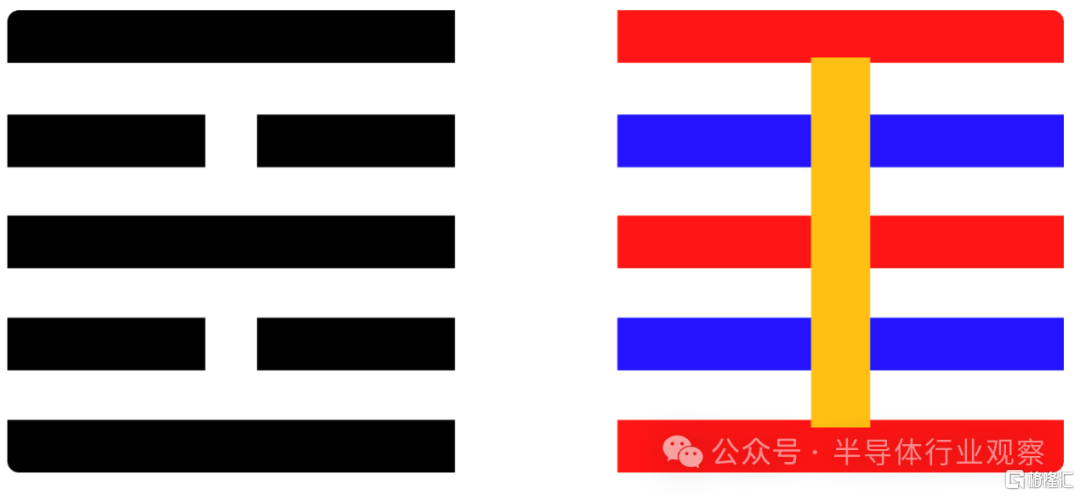

图1:SAQP流程

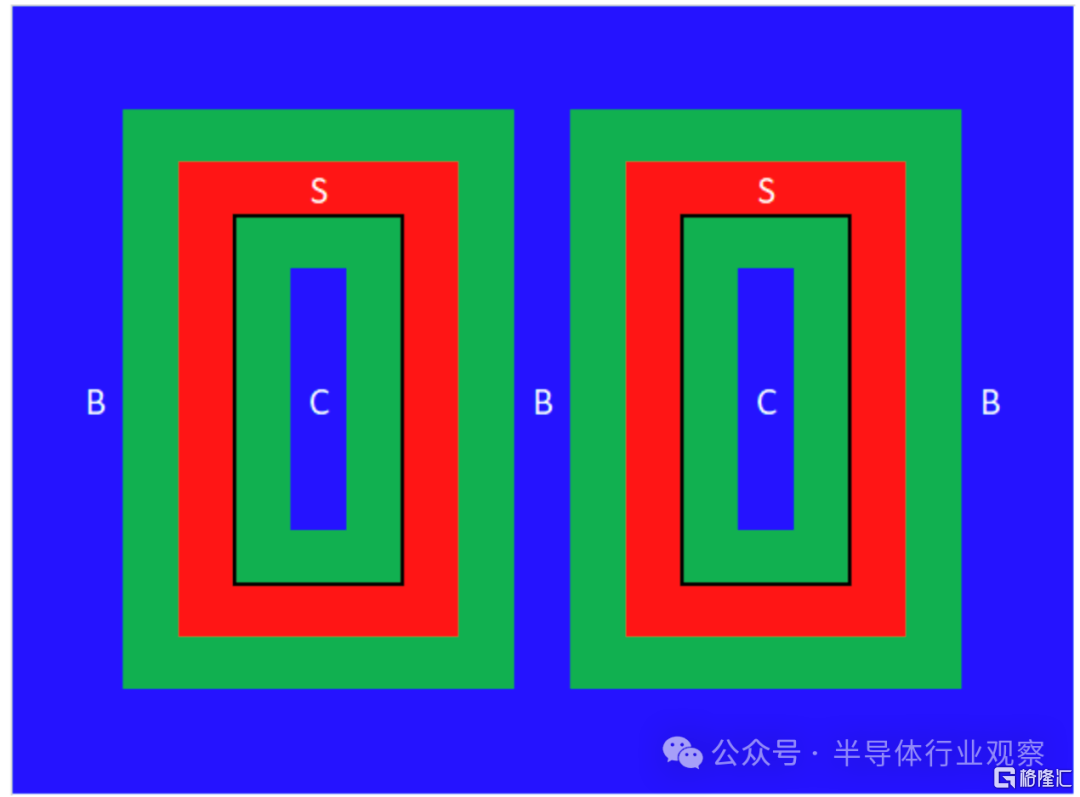

该过程自然地将特征(features)分为三组:核心(core)、外壳(shell)、边界(boundary)(图 2)[4]。外壳自然形成需要切割的环。同样,边界构成一个网格,也需要将其分成多个段。因此,SAQP 过程必须以光刻步骤结束,该步骤切割或修剪先前定义的壳和边界特征。相比之下,较旧的 SADP 流程只有两个组:核心组和边界组。

图 2. 将 SAQP 生成的特征分为核心 (C)、外壳 (S) 和边界 (B) 类别。绿色表示第二个垫片(spacer)。核心和边界特征预计由相同的材料制成,而壳特征由不同的材料制成。

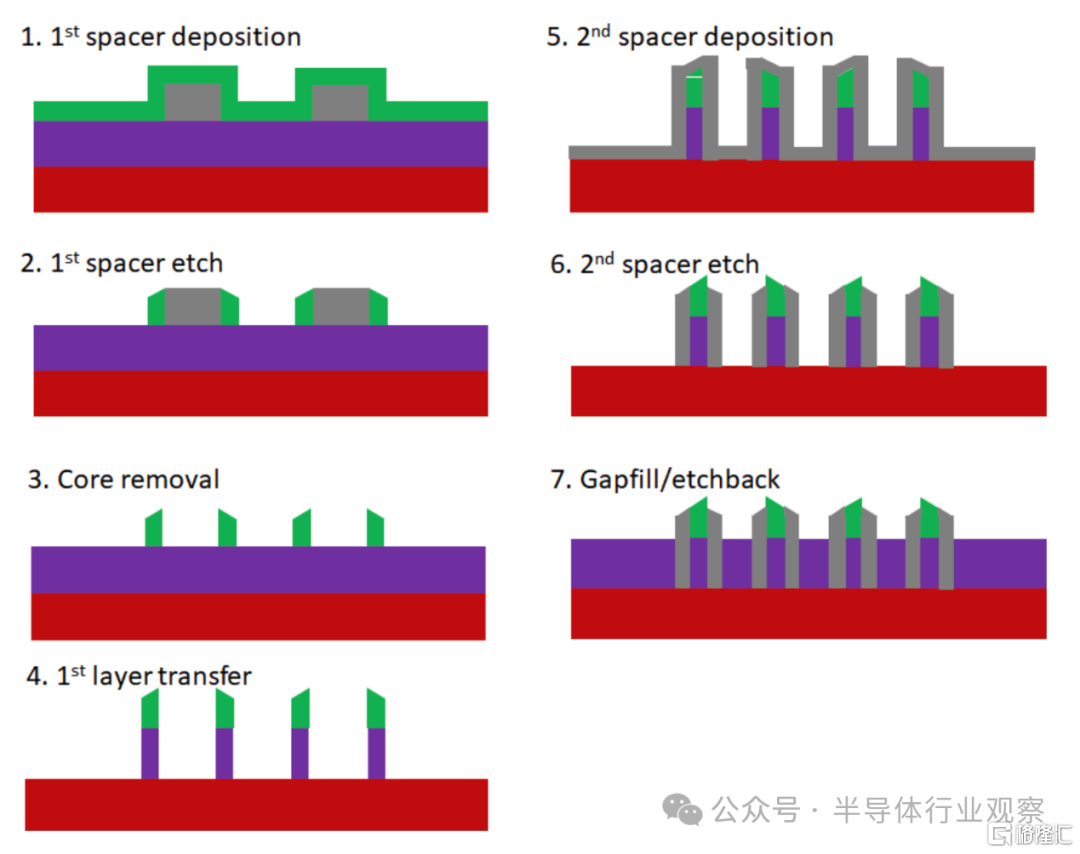

在另一种 SAQP 工艺流程下(图 3),壳特征实际上是剩余的第一间隔材料(first spacer material),而核心和边界是不同的材料,要么是基板,要么是间隙填充材料。因此,它们在图 2 中用不同的颜色表示。它们是不同材料的事实表明它们可以被选择性蚀刻。这为一些难以完成的图案化提供了机会。

图 3. 替代 SAQP 工艺流程,其中不同的材料填充不同的区域,而不是间隙。

一个特别方便的应用是最小节距和 2x 最小节距功能的组合。在k1<0.5的单次曝光中通常禁止这种组合。一种特别令人望而却步的组合是最小节距的线,以及 2 倍最小节距的中断(图 4,左)。断线的衍射图样比线本身的衍射图样信号弱得多,因为它们占据的面积要小得多。散焦时它的性能也会下降得更快 。这种组合也不能用辅助特征来固定,因为没有空间插入它们以获得最小节线。另一方面,通过选择性蚀刻,掩模特征可以穿过中间的介入线(图 4,右)。这极大地简化了切割,并避免了在两个位置进行单独切割时可能出现的边缘放置错误 。

图 4. 左:行距和断行距(=2X 行距)不兼容。右图:不兼容的间距可以在选择性蚀刻的帮助下结合起来。在这种情况下,只有蓝色区域的材料被蚀刻;红色区域不受此遮罩的影响。

对于选择性蚀刻,必须使用三个掩模 - 一个需要定义分离的 A/B 区域,第二个掩模用于 A 选择性蚀刻,第三个掩模用于 B 选择性蚀刻。然而,选择性蚀刻(与 SAQP 结合)还允许更大的重叠容差和最小数量的掩模,从而允许最小线间距和间隔为最小线间距两倍的线中断的组合,从而使多重图案化变得更容易处理。

总结而言,所有自对准多重图案化工艺均包含以下步骤:

打印心轴轨迹(mandrel tracks)。

在打印的心轴图案的侧面生长侧壁(sidewalls)。

移除心轴图案。

在侧壁之间开发最终制造的图案。

添加介电块(dielectric blocks)以在最终目标中创建所需的尖端到尖端(tip-to-tip)间距。

写在最后

随着我们迈向更先进的技术节点,具有更激进的节距(例如 32 纳米)的关键后端(BEOL)金属层的图案化变得非常具有挑战性。通常,在这些 BEOL 层中创建沟槽,然后在最终金属化步骤中用金属填充沟槽。为了在连续沟槽中产生断开,添加了垂直于沟槽的阻挡层,从而形成小的金属尖端到尖端。

在行业中,人们考虑了各种选择来对最具侵略性的 BEOL 层和块进行图案化。一种选择是结合使用浸没式光刻和所谓的金属线自对准四重图案化(SAQP),以及块层的三重图案化。然而,该选项需要三重块掩模和三重光刻工艺流程,这增加了所提出的解决方案的成本和复杂性;另一种选择是直接使用 EUV 光刻 (EUVL) 在一次曝光中对 BEOL 金属层进行图案化。尽管这种直接 EUVL 集成流程非常简单且具有成本效益,但图案保真度(例如图案的形状)和图案可变性以及掩模制作预计将极具挑战性,特别是对于非常小的尖端到尖端(tip to tip)。

所以,大家对于彭博社这个观点怎么看啊?

下载格隆汇APP

下载格隆汇APP

下载诊股宝App

下载诊股宝App

下载汇路演APP

下载汇路演APP

社区

社区

会员

会员