2022年11月,ChatGPT的爆红引发了行业对大算力芯片的渴求,英伟达受益匪浅,迅速向台积电追加了上万片CoWoS封装订单,台积电也由于产能不足随即宣布扩产。不仅是CoWoS,近年来,以此为代表的Chiplet封装(又称芯粒集成封装)技术成为行业的热点话题,甚至被认为是后摩尔时代中国半导体弯道超车的重要机遇。Chiplet封装究竟是什么?为什么在行业中有如此高的认可度?这项技术未来的应用前景如何?

CIC灼识咨询近期针对火热的先进封装赛道进行了深度的剖析和研判,并着重研究了Chiplet封装,将于近期发布《全球先进封装行业研究报告》,本期文章摘录其中部分内容,以飨读者。

01 行业患上算力“饥渴”症

随着2022年ChatGPT 3.5的成功,掀起了AI大模型的浪潮,也意味着全球步入了人工智能的更高阶段——不只是一个聊天机器人,比尔·盖茨将ChatGPT的发布比作互联网的发明,并认为它同样可以改变世界,英伟达CEO黄仁勋也在GTC(GPU Technology Conference)2023上三次提到“AI迎来iPhone时刻”。

在众多大模型百花争艳的背景下,算力作为大模型“智商”的物理载体,其重要性不言而喻,人类社会对算力的需求也更上一个台阶。近年来,全球算力规模稳步增长,根据中国信通院数据,2018年全球算力规模约232.0EFlops,2022年达891.8EFlops,年均复合增长率达到40.0%。而其中智能算力规模在AI大模型训练和推理的需求拉动下,更将快于整体算力的增长。也难怪屡屡有新闻报道各下游企业“抢货”,行业似乎患上了算力“饥渴”症。

如何提升芯片性能成为半导体行业的重点课题,然而仅通过先进制程提升芯片性能这条路似乎没有那么顺畅。

02 先进制程的难题

在半导体产业发展的历史上,先进制程一直扮演着关键角色,通过提升单位面积上集成电路可容纳的晶体数量提升芯片的性能。

自上世纪60年代以来,半导体行业一直遵循摩尔定律,通过不断发展微缩工艺向着提升晶体管密度的方向不断进步。然而,近年来先进制程在向新一代关键节点的进展屡屡落后于摩尔定律的预期。例如在5nm向3nm迈进的节点,各大晶圆厂进展均受阻。以台积电为例,本应在2022年量产的3nm工艺直至2023年才得以量产,且晶体管密度仅为5nm的1.6倍左右。如果要到达接近两倍晶体管密度,则需要等到2024年的增强版工艺量产。

无论是时间还是性能,近年的制程发展都低于摩尔定律的预期。单靠先进制程似乎难以跟上AI大模型的需求。

究其背后原因,光罩尺寸限制了芯片面积的增加,也就使得晶体管数量无法通过提升芯片面积而增长。而量子隧穿效应和成本随更高制程的急剧增长也同样是先进制程发展的关键制约因素。

那么,在先进制程之外,是否还有其他手段可以与先进制程共同提升芯片算力呢?

03 集成芯片模式另辟蹊径

集成芯片是自上而下的构造设计方法,它将整个芯片系统划分为多个独立裸片(即芯粒,Chiplet),其中每一个裸片功能独立,可以独立设计、制造和测试,最后通过封装的方式将所有裸片封装在一起形成完整功能的芯片系统。这种设计构造方法可以提高芯片开发的灵活性、可扩展性和效率。

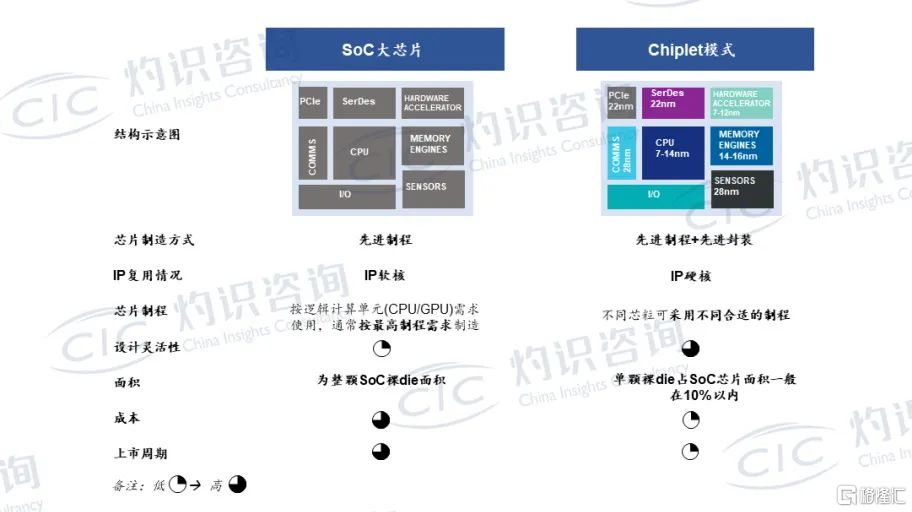

与传统的SoC这种单芯片设计构造模式相比,集成芯片可以实现更大的芯片尺寸,突破目前的制造面积局限,推动芯片集成度和算力持续提升。其次,集成芯片中小芯片的互联引入了半导体制造加工技术,无论是连接还是延迟,都接近于芯片,使得整个集成芯片能达到类似单颗芯片的效果,可以突破单芯片集成下功耗墙、内存墙等的限制,能够持续优化芯片系统的性能和功耗。此外,集成芯片相较于传统的SoC展现出在性能、设计灵活性、生产成本和产品上市周期方面的显著优势。这是因为集成芯片提供了一种全新的视角,通过分散式设计,将各计算小单元按照各自的制程需求进行独立制造,从而提高设计灵活性,降低生产成本。不同芯粒可用不同的工艺制程完成,突破单一工艺的局限。

SoC大芯片与集成芯片模式的比较

来源:CIC灼识咨询

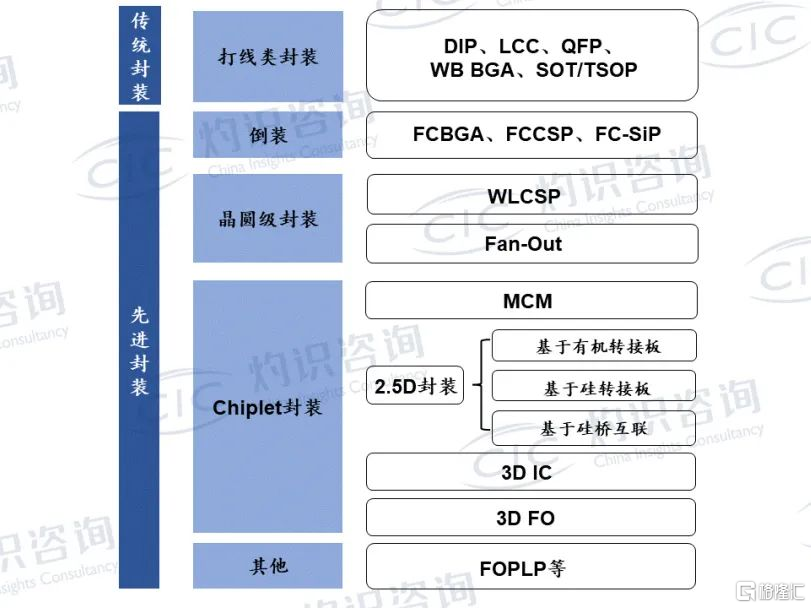

04 从先进封装到Chiplet封装

先进封装是自采用Bumping代替引线键合以来的概念,囊括了众多封装技术类型,代表着行业逐渐理解到,需要采用更先进的设计和工艺对芯片进行封装级重构,以提升整体的性能。但行业真正对先进封装如此重视的原因,则是由于其中的Chiplet封装(又称芯粒集成封装)技术。

Chiplet封装技术是实现集成芯片的主要手段,作为一种半导体制造技术,它使得集成芯片无论连接和延迟,都接近于芯片而不是 PCB 或者有机基板,最早做这项工作的也是台积电等芯片制造厂商。Chiplet封装是先进封装的重要组成部分,更是实现集成芯片构造的途径。它将芯片的集成维度从晶圆维度提升至芯粒维度,打破了光罩尺寸对于芯片尺寸的限制,也一定程度上克服了先进制程的局限,是日益增长的芯片性能需求与摩尔定律逐渐受挑战的双重作用下的最优解,其技术平台的发展见证了半导体产业随下游应用市场发展的又一次重要革新。从先进封装到Chiplet封装概念,背后反映的是行业理解的巨大进步。

主要封装方式分类

来源:CIC灼识咨询

在各种先进封装类型中,Chiplet封装中的2.5D封装、3D IC和3D FO代表了先进封装行业中最领先的技术。这些封装技术实现了芯片与芯片间高密度信号互联,提升信号互联密度,缩短信号互联距离。这种高密度互联为集成芯片提供了更紧凑和高效的可能性,以实现更高的集成度、更低的功耗和更快的数据传输速度。

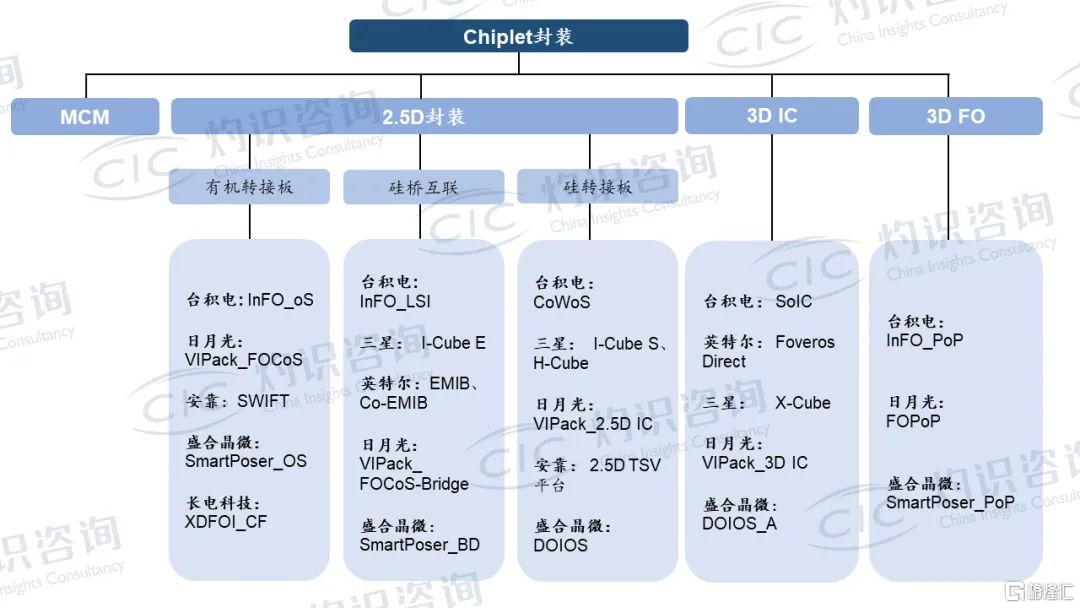

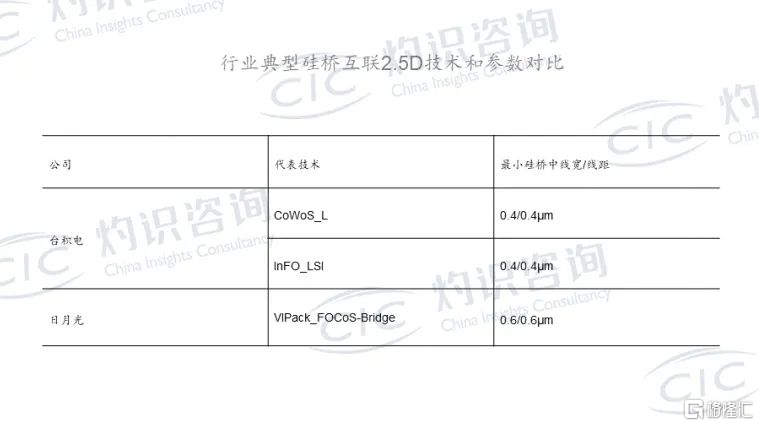

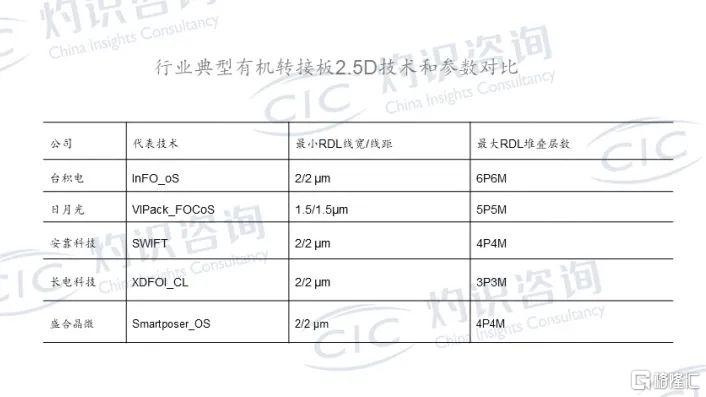

2.5D封装从技术路线来看主要可分为有机转接板、硅转接板和硅桥互联,不同的技术路线由于实现的连接密度不同,其对应的应用场景也有一定差异。其中,有机转接板的代表性技术平台主要包括台积电的InFO_oS和CoWoS_R、日月光VIPack技术平台的FOCoS、安靠的SWIFT、长电的XDFOI_CL和盛合晶微的SmartPoser_OS。硅转接板的代表性技术平台主要包括台积电的CoWoS_S、三星的H-Cube和I-Cube S,以及盛合晶微的DOIOS等。硅桥互联的代表性技术平台主要包括台积电的InFO_LSI和CoWoS_L、三星的I-Cube E、英特尔的EMIB和Co-EMIB、日月光VIPack技术平台的FOCoS-Bridge和盛合晶微的Smartposer_BD等。

3DIC封装在垂直的方向堆叠更多的小芯片,利用在z轴空间立体的延伸,有效降低体积和重量、提高硅片效率、降低功耗和减少信号延迟降低噪声。其代表性技术平台主要包括台积电的SoIC、英特尔的Foveros、三星的X-Cube、日月光的VIPack_3D IC和盛合晶微的DOIOS_A等。

3D FO是适用于三维多芯片异质集成的新型扇出型封装技术,其综合运用多种规格的重布线、凸块以及高铜柱等水平和垂直方向的互联工艺,实现多芯片之间高密度的电气互联,以及多层芯片的三维堆叠整合,缩短了信号传输路径,减少了信号延迟并降低了信号噪声,同时大幅减小了封装结构的体积。其代表性技术平台主要包括台积电的InFO_PoP、日月光的FOPoP和盛合晶微的SmartPoser_PoP等。

Chiplet封装主要技术平台

来源:CIC灼识咨询

Chiplet封装技术涉及众多前道晶圆制造技术,因此拥有前道晶圆制造的背景和经验非常重要。大量先进工艺包括TSV、RDL、微凸块和混合键合等都广泛应用于Chiplet封装,这些工艺均需要使用类似前道晶圆制造的技术,对设备、无尘室等级和技术精度等都有较高的要求,从目前行业的领先企业来看,例如台积电、英特尔、三星电子和盛合晶微等企业无不拥有晶圆制造的背景和经验。

05 台积电引领Chiplet封装行业发展

早在2009年台积电就开始布局Chiplet封装,投入巨额资金对相关技术进行研发,并于2011年发布了基于硅转接板的2.5D CoWoS封装平台并获得了赛灵思的订单。2013年,赛灵思和台积电共同宣布了全球首个正式量产的2.5D封装产品Virtex-7 HT系列,这款芯片是世界上首款异构All Programmable器件,内含多达16个28Gbps收发器和72个13.1Gbps收发器,是当时唯一符合光传输网络中高带宽、高速Nx100G和400G 线卡应用的单一封装解决方案。2016年,台积电推出了行业中首款3D晶圆级扇出封装InFO_PoP,并凭借这项技术长期独占苹果手机芯片订单。

在CoWoS封装诞生的起初数年里,曾由于价格昂贵而订单不足,但ChatGPT之后,价格不再是困扰,下游应用对芯片性能的渴求成了决定性因素,CoWoS封装因此一跃成为英伟达高性能算力芯片的一选。

在台积电引领Chiplet封装的行业发展的背景下,同行业企业也在积极跟随行业发展趋势。从台积电、英特尔、三星和盛合晶微等具有晶圆制造背景的厂商,到安靠、日月光和长电科技等仅具有封装背景的厂商,都在向着高密度、高集成度和高性能的方向发展自己的Chiplet封装技术。

众所周知,大陆在先进制程方面与领先企业台积电等还有着不小的差距,庆幸的是,大陆目前在Chiplet领域也有所建树。例如从CoWoS平台来看,国内盛合晶微DOIOS平台是大陆首个基于硅转接板2.5D封装的量产平台,为众多高性能算力芯片设计企业提供了另一选择。

06 Chiplet封装技术指标详解

Chiplet封装是先进封装的前沿工艺,可实现多维异质集成功能,其通过并排或堆叠的方式对多颗裸芯片进行高密度互连,并集成到同一封装模块中,进而实现提高集成电路系统集成度的效果。

2.5D封装是Chiplet封装的代表。2.5D封装主要指的是将芯片并列放在有机转接板、硅转接板上或通过硅桥互联,利用RDL和微凸块连结使得转接板之内的金属线可连接不同芯片的电子信号;再连结下方的金属凸块等,最终实现多芯片与封装基板之间更紧密的互连。

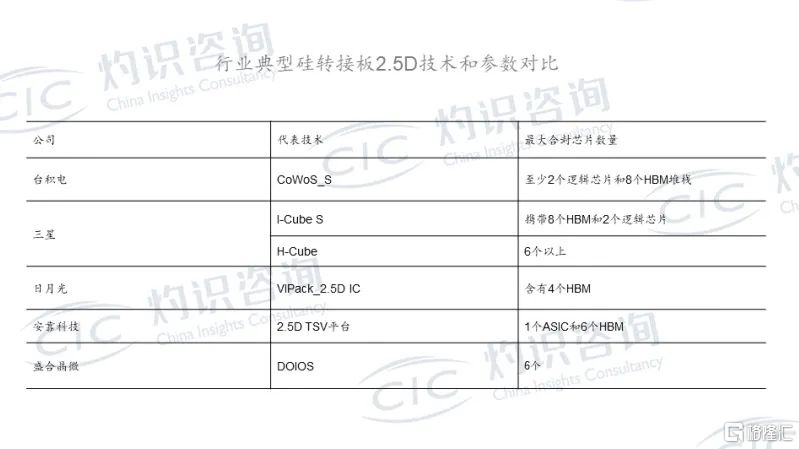

2.5D封装中使用硅转接板的代表技术包括台积电的CoWoS_S、三星的I-Cube S等,衡量其的关键技术参数包括最小微凸块间距、最大转接板尺寸和最大合封芯片数量等。

来源:CIC灼识咨询

基于硅桥互联的2.5D封装利用带有路由层的微小硅片作为小芯片之间的封装内互连,将硅桥嵌入在扇出RDL层中达到高密度互联效果。通过不再使用硅转接板作为中间介质的方式,消除由转接板尺寸所带来的封装尺寸的限制,以获得更好的灵活性和更高的集成度。

来源:CIC灼识咨询

基于有机转接板的2.5D封装是一种具有成本效益的平台,可通过基于 RDL 的工艺实现高带宽和高密度的芯片到芯片互连。台积电是这种技术主要推动者之一,其InFO系列是面向高集成度需求、网络和 HPC 应用的高性能解决方案;ASE、JCET和Amkor等也已陆续开发出具有巨大竞争潜力的类似解决方案。

来源:CIC灼识咨询

随着人工智能、自动驾驶、5G网络、物联网等新兴产业的进一步发展,芯片对于3D IC封装的需求越来越强烈。3D IC封装是指在三维空间组装芯片,在垂直的方向堆叠更多的小芯片,从而集成更多的功能。3D IC封装利用在z轴空间立体的延伸,有效降低体积和重量、提高硅片效率、降低功耗、减少信号延迟并提高信号完整性,也是行业领先企业目前发展的重点。

07 结语

到此,我们可以圆满地解释开头的问题, Chiplet封装技术平台解决了先进制程发展的痛点问题,将芯片集成维度提升至芯粒维度,提升了算力芯片内的互联密度,进而提升芯片性能和功能集成度,在大模型时代背景下助力芯片设计企业及下游应用企业向更高的算力进发,将半导体产业发展推向新的高潮。

那么,先进封装及Chiplet封装的市场规模有多大呢?市场的潜力如何?从芯片设计到实现,有哪些行业玩家参与其中?技术流程上,有哪些关键步骤?市场竞争格局又是如何?对于这些关键问题,请关注CIC灼识咨询推出的《全球先进封装行业研究报告》。

下载格隆汇APP

下载格隆汇APP

下载诊股宝App

下载诊股宝App

下载汇路演APP

下载汇路演APP

社区

社区

会员

会员