台积电要在5nm及更先进制程保持领先,EUV光刻机是重要一环,近年来,该公司不断购入EUV设备,以维持先进制程产能优势。台积电于日前召开技术论坛,指出其EUV设备累计装机数量到2020年已占全球总数的50%,到2020年为止,采用台积电EUV技术生产的晶圆,占全球EUV光刻晶圆数的65%。而随着制程推进至5nm,每片晶圆采用EUV掩模层大幅拉升,台积电预估2021年EUV掩模产能将是2019年的20倍。

今年下半年,台积电5nm产能进一步提升,包括苹果A15应用处理器及M1X/M2计算机处理器、联发科及高通新款5G手机芯片、AMD Zen 4架构计算机及服务器处理器等将陆续导入量产。台积电为了维持技术领先,由5nm优化后的4nm将在明年进入量产,全新3nm也将在明年下半年导入量产。

下面具体看一下这些需要用到EUV设备的先进制程情况。

台积电5nm于2020年量产,2023年,包括4nm的5nm系列制程产能将会比2020年大幅增长4倍。此外,台积电还推出了5nm家族的最新成员-N5A制程,目标在于满足汽车应用对于运算能力日益增加的需求。

位于台南的晶圆18厂第1、2、3、4期是5nm生产基地,其中,第1、2、3期已经开始量产,4期兴建中。

5nm家族中的4nm加强版由于减少了掩模层数,以及与5nm几近兼容的设计法则,进一步提升了效能、功耗效率、以及晶体管密度。4nm工艺将把芯片尺寸收缩 6%,同时带来功耗和性能上的进一步改善。

3nm方面,将增加EUV的使用量,效能将比5nm提升10-15%,功耗减少25-30%,逻辑密度增加1.7倍,SRAM密度提升1.2倍、模拟密度则提升1.1倍。

2nm方面,台积电将在新竹市新建一座 Fab 20 工厂,用于2nm系列制程工艺的生产。尽管当前仍在忙着征地,但该公司已经为 Fab 20 工厂的初期生产规划了四个阶段。

随着以上最先进制程晶圆厂在未来1~3年内逐步完成建设并投入量产,以及美国亚利桑那州12吋厂第一期在2024年后进入量产,采用台积电EUV技术的晶圆数将快速增长,其在EUV设备上的投资将越来越大。

01

对手虎视眈眈

目前,作为台积电在先进制程领域的唯一对手,三星一直在努力追赶中,这给台积电带来了不少压力,无论是技术层面,还是在成本层面,都需要不断优化,才能保持对三星的优势。

三星预计2021年将在半导体设施上投资35万亿韩元,创历史新高,比2020年的28.9万亿韩元增长20%。股票分析师预计,该公司将在存储芯片上花费24万亿韩元,在系统半导体上花费11万亿韩元。

三星不仅将在韩国投资,还将在美国和中国投资。在韩国,其在平泽的工厂将转变为存储器和系统半导体的生产基地。晶圆代工生产线于今年年初投入使用,预计将于下半年开始运营。此外,预计该公司将在2021年完成3号工厂的建设,该工厂将生产内存和晶圆代工产品。

另外,三星还计划在美国投资170亿美元建设新晶圆厂,用于生产5nm及以下先进制程芯片。这主要针对的就是台积电在美国的5nm新厂。

三星扩建最先进制程晶圆厂,同样需要大量的EUV设备。为此,不久前,韩国总统文在寅和荷兰首相马克·吕特举行了虚拟峰会,期间,关于与ASML的深入合作是一项重要议题。双方的声明中写道:“两国同意加强在半导体供应链方面的合作,相互承认对方是半导体领域的核心合作伙伴。”

对于寻求在全球半导体竞赛中保持领先地位的韩国芯片制造商,特别是三星来说,ASML的EUV设备至关重要。三星电子副董事长李在镕去年 10 月访问了ASML,显然是为了获得 ASML的EUV光刻机。

5月,ASML与韩国中央和地方政府签署了一份谅解备忘录,将投资 2400 亿韩元(2.111 亿美元),到 2025 年在京畿道华城建立 EUV 产业集群。

据日本专家分析,2020年,当5nm大规模生产及3nm试产启动时,台积电需要35台新EUV光刻机。到2021年,5nm生产规模扩大,3nm风险生产将启动,所需的新EUV光刻机数量达54台;到2022年,当3nm大规模生产、2nm试产启动,需要的新EUV光刻机数量为57台。

三星方面,李在镕在2020年访问ASML期间要求的“2020年9台EUV光刻机”中,至少有4台将2020年抵达三星,其余5台在2021年初引入。尚不清楚2021年后是否会落实每年20台EUV设备,但实际数字相差不会很大。

根据假设得出的结论,台积电在2021-2015年间总共需要292台EUV光刻机,每年平均需新增58台。三星每年需要20台,一共需要近80台。这将是一笔庞大开支。

02

台积电压力山大

对于台积电来说,虽然其先进制程,特别是5nm目前无敌于天下,但客户对于使用4nm或全新3nm态度还不够明朗,主要原因是成本太高,而其决定因素是EUV掩模层数不断增加,再加上EUV设备本身就是高成本,两个因素叠加,直接提升了晶圆代工价格。

由于先进制程投资金额愈来愈高,能够支付如此庞大晶圆代工费用的半导体厂已经没有几家,虽然台积电现在有苹果、NVIDIA、AMD、高通、联发科、英特尔、博通、Marvell、赛灵思(Xilinx)等大客户采用先进制程,但随着三星晶圆代工积极扩产,英特尔加码先进制程产能投资,台积电面临的竞争压力越来越大。

为了在明年之后加速客户5nm产品线转换至3nm,据悉,台积电将启动EUV持续改善计划(Continuous Improvement Plan,CIP),希望在略为增加芯片尺寸的同时,减少先进制程EUV掩模使用层数,以降低3nm成本。

EUV光刻机价格越来越高,ASML在下半年即将推出的最新机型NXE:3600D,其价格高达1.4~1.5亿美元,产出吞吐量每小时可达160片12吋晶圆,与上代机型相比,产能增加幅度不大。而由制程来看,4nm由5nm优化而来,EUV掩模层大约在14层以内,但3nm预计将采用25层EUV掩模,因此,3nm晶圆代工价格恐怕会达到3万美元,并不是所有客户都愿意买单。

为了加快客户产品线由5nm向3nm的推进速度,台积电启动EUV CIP计划改善制程,希望透过减少EUV掩模层使用道数及相关材料,例如将3nm的25层EUV掩模层减少至20层,虽然芯片尺寸将因此略为增加,但若计划成功可以有效降低生产成本及晶圆价格。若能有效减少3nm晶圆EUV掩模层数,在达成同样产出量情况下将有助于减少EUV设备采购量,若每年少采购1~2台EUV设备,资本支出也可降低3亿美元。

台积电的成本压力,从最近发布的第二季度财报也可见一斑。其单季税后纯益 1343.6 亿元新台币,季减 3.8%,年增 11.2%,每股纯益 5.18 元,低于市场预期。第二季营收 132.9 亿美元,季增 2.9%,年增 28%,毛利率 50%,季减 2.4 个百分点,年减 3 个百分点,营益率 39.1%,季减 2.4 个百分点,年减 3.1 个百分点;税后纯益 1343.6 亿元,季减 3.8%,年增 11.2%。

另外,上半年营收 262.08 亿美元,新台币营收 7345.55 亿元,年增 18.2%,毛利率 51.2%,年减 1.2 个百分点,营益率 40.3%,年减 1.5 个百分点。

总体来看,营收增长,但利润下降了,这其中很重要的原因就是在先进制程上的投资巨大,难以被营收抵消。

以制程来分,台积电第二季 5 nm制程出货占晶圆销售金额的18%,7 nm为 31%,16 nm为 14%,28 nm为 11%。可见,5nm占比很大,仅次于7nm,这同时说明其需要在这方面投入巨资,才能实现这样的量产水平,但相应的回报与投入并不呈线性关系。

基于以上这些因素,台积电要想继续发展最先进制程,同时保持竞争力,不至于内对手缩小差距,就必须在成本控制方面多下功夫了。

03

多渠道降本增效

除了减少EUV光刻机采购数量及掩模层数外,还可以有多种方法降低最先进制程的成本,同时保证良好的性能。

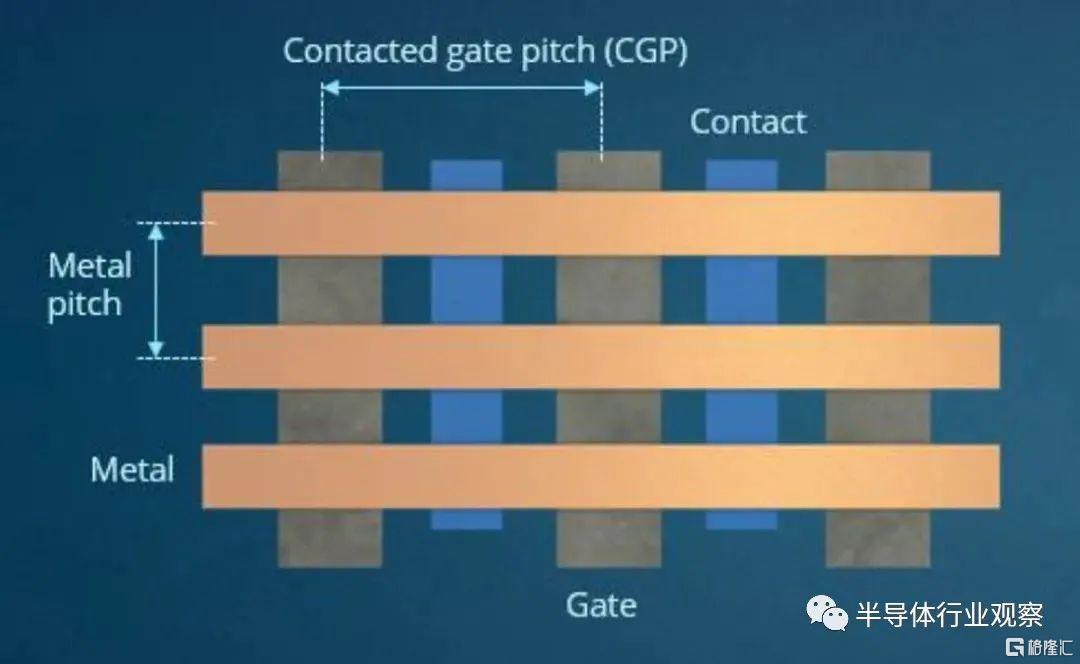

例如,可以通过设计和技术协同优化(DTCO)减少器件占用空间。逻辑器件是许多逻辑单元的组合,这些逻辑单元执行基本逻辑功能。每个单元都具有多个晶体管栅极,这些晶体管栅极由金属线连接。垂直排列的门之间的距离称为接触门间距(CGP)。水平连接栅极的金属线之间的距离称为金属间距。通过乘以两个间距,可以估计单元单元的一个区域。

传统上,业内使用光刻图案来精细化栅极和导线,通过更紧凑的方式缩放,这称为内在缩放。但是,随着制程节点的推进,进一步缩短栅极和导线距离的物理空间正在迅速消失。此外,如果电气器件和结构太密集,信号可能会干扰,从而降低器件的性能和功率特性。

设计与技术的协同优化(DTCO)可实现与以往不同的缩放技术,这被视为未来节点的总体缩放优势,因此备受关注。其旨在将新材料和材料工程技术与逻辑设计师的出色理念相结合,在不改变光刻或间距的情况下降低每个区域的成本。

DTCO 是一种从设计和技术两方面进行优化的方法。利用DTCO,可将更多的功能塞进逻辑单元的有限区域。

为了在提高 PPAC(功耗、性能和每面积成本)的同时实现可靠性和产量,必须保持边缘的线性度和平滑度。事实上,任何图案形状在边缘上通常都会发生粗糙度和不均匀性,但传统上,由于边缘在图案线宽中所占的比例非常小,因此这种扰动基本上可以忽略不理。但是,随着 EUV 缩放的推进,边缘占据线宽 30% 的情况并不少见。边缘粗糙度是一个严重的问题。光刻分辨率和线边缘粗糙度问题愈加突出。

目前,创新的集成材料解决方案正在出现,这些解决方案在纳米级响应这些挑战,并成功地实现 EUV 双图案化。

总之,使用DTCO 可以继续推进先进制程,同时提高PPAC。

04

结语

当制程发展到3nm,台积电这样的龙头企业也对成本愈加敏感,需要采取有效方法把成本降下来,除了以上提到的几点方法之外,产业链上下游厂商也在探索更多、更好的方法,以求将摩尔定律继续推进下去。

下载格隆汇APP

下载格隆汇APP

下载诊股宝App

下载诊股宝App

下载汇路演APP

下载汇路演APP

社区

社区

会员

会员