作者:畅秋

来源:半导体行业观察

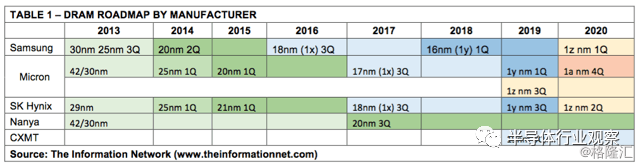

DRAM制程工艺进入20nm以后,由于制造难度越来越高,内存芯片制造厂商对工艺的定义已经不是具体的线宽,而是分成了1x、1y、1z,大体来讲,1x-nm制程相当于16~19nm、1y-nm相当于14~16nm,而1z-nm则相当于12~14nm。

2019年3月,三星宣布研发出第三代1z-nm的8Gb DDR4,而且无需使用极紫外光刻(EUV)设备和工艺(未大规模采用,但在一些关键环节很可能还是需要用到EUV的)。

另一家巨头美光科技则是在今年8月宣布大规模生产1z-nm 16Gb DDR4,其也未使用EUV。

在三星、美光之后,SK海力士也推出了16Gb DDR4内存芯片,预计明年开始大规模出货。在能效方面,SK海力士称其1z-nm工艺与上一代的1y-nm 8Gb DRAM相比,生产效率提升了27%;功耗降低了40%。SK海力士透露,他们在1z-nm制程上引入了新设计思路,提高了芯片的稳定性。SK海力士在新闻稿中特别提到:1z-nm制程工艺不会使用EUV。

而从这三家巨头的发展来看,采用1z-nm制程的LPDDR5、HBM3等也将很快推出。

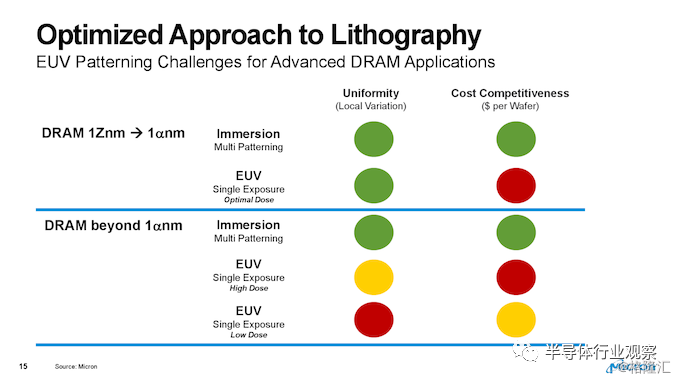

与当前被广泛使用的193nm波长深紫外光DUV工艺相比,EUV设备的波长为13.5nm,这在很大程度上提升了该种设备的制造难度,目前,一台EUV光刻机的价格超过1亿美元。

除了购机的CAPEX成本外,EUV设备在实际应用当中还要面临很多技术和成本挑战及障碍,这些都使得生产效率偏低,提升起来非常困难。因此,在现阶段,芯片制造商,特别是先进DRAM厂商,与高性能的CPU、GPU、手机SoC,以及FPGA相比,DRAM对成本更加敏感,因此,相应的芯片制造商会都尽可能地避免使用EUV,即使用,也会控制在一定范围内。

目前,主要的DRAM厂商,如三星、美光和SK海力士,它们最先进的1z-nm制程工艺都没有大规模使用EUV。因此,EUV要想大面积普及,还需要在性能和综合成本方面有所提升。

那么,在不使用EUV设备的情况下,顶级的DRAM厂商的先进制程工艺及其产品具体是什么样的?下面就来看一下吧。

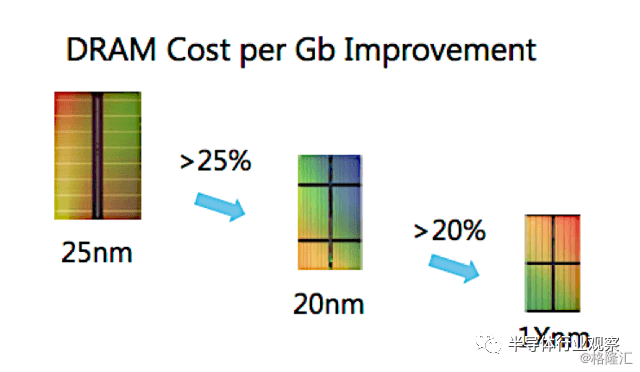

今年3月,三星电子宣布推出第三代1z-nm的8Gb DDR4,该公司表示,最新的8Gb DDR4是在采用1y-nm工艺的第二代芯片量产后16个月内开发的。据悉,该1z-nm 8Gb DDR4与上一代1y-nm相比,生产效率提升了20%多,这意味着在相同的良率和生产周期情况下,生产成本将显着降低。三星称2020年即可实现大规模量产,主要用于企业服务器和高端PC。

三星表示,开发1z-nm DRAM为IT行业过渡到下一代DRAM(如DDR5、LPDDR5和GDDR6)铺平了道路。

传统上,三星不会透露新存储芯片的制程工艺细节,因此,目前还没有其最新DRAM芯片几何形状的具体数据信息,但结合1z-nm制程节点的特征来看,可以推测其最小线宽会低于15 nm。

而在不使用EUV的情况下,三星会继续使用ArF(氟化氩)浸没式光刻工具,在浸没式光刻的情况下,超薄节点需要多patterning处理,因此,三星很可能是将这种方法与各种技巧结合使用,以确保芯片良率和性能。

这里要强调的是,三星只是未大规模使用EUV制造DRAM芯片,但在一些环节上,离开了EUV还是寸步难行。

今年6月,有知情人士透露,三星电子将首次在DRAM上使用EUV。

据悉,三星将EUV首先应用在接触位线的BLP层上。位线基本上用作中央数据通道。通过这样做,芯片制造商可以减少构图步骤,从而降低成本。

三星的B-die内存采用的是20nm制程工艺,而新的A-die和M-die会使用三星1z-nm工艺,存储密度更大,B-die的单die容量只有8Gb,而A-die则可以做到16Gb或32Gb,也就是2GB或4GB的容量,这使得单面32GB的内存将成为可能。

如下图所示,美光科技从2017年第三季度开始在1x-nm节点进行了五个季度的生产之后,从2019年第一季度的1y-nm节点迅速转移到了2019年第三季度的1z-nm节点。

根据Information Network的报告,截至2019年9月,美光9%的DRAM采用20nm制程,在1y-nm节点上,美光的产量占15%,略低于SK海力士,但领先于三星。而该公司量产的DRAM中有6%采用了最先进的1z-nm制程工艺。

与上一代1y-nm相比,美光的1z-nm 16Gb DDR4产品可提供更高的位密度,性能增强的同时,降低了成本。

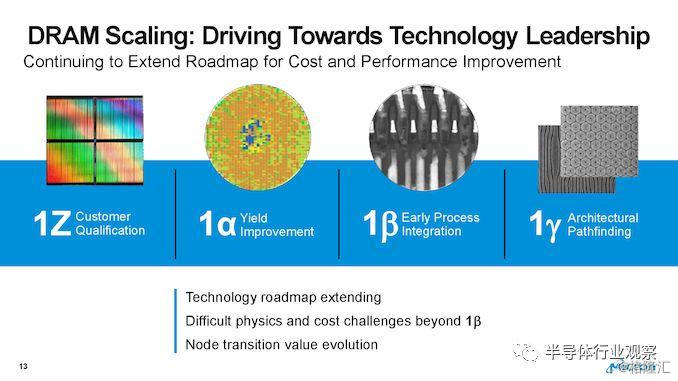

随着扩展新制造技术的难度越来越大(在工程和财务方面都有挑战),美光与所有DRAM制造商一样,将推出更先进10nm级节点制程,在1z-nm之后,还计划引入至少三个10nm级的制程,分别是1α-nm、1β-nm和1γ-nm(希腊字母γ,不是英文中的y)。这些将通过使用逐渐减小的单元尺寸来增加芯片产量。例如13 nm、12 nm和10~11nm。

迄今为止,美光宣布的所有10nm级节点均依赖于具有双,三或四patterning的深紫外光刻(DUV),而多patterning需要更多的工艺步骤,这会延长生产周期,因此需要更多的光刻工具和洁净室空间来维持现有的产量。

以目前每12个月增加一个新节点的速度,如果所有节点均按计划进行,就引入新节点而言,美光的多patterning路线图至少可以扩展到2023年。而按照每种新工艺技术至少要使用三到四年的规律计算,可以肯定地说,美光计划在未来很多年内使用多patterning的DUV技术。

同时,该公司承认有在物理和成本方面面临着极大的挑战,特别是1β-nm工艺与四patterning浸没式光刻技术方面,因此,这些前沿制程工艺将带给市场什么还有待观察。

在使用EUV这个问题上,美光正在评估ASML的Twinscan NXE步进扫描以及使用极紫外光刻技术生产所需的其他设备的功能,并正在评估这些工具何时才能制造DRAM。

用于DRAM制造的话,EUV不仅在逻辑上面临挑战,而且在一致性和成本方面也面临着挑战,美光认为:目前,EUV工具只有在发射高剂量的EUV辐射(在单一patterning情况下)时,才能保证可接受的均匀性,这会将芯片成本提高到不可接受的水平。因此,美光没有立即使用EUV的计划,但正在密切关注其演变和发展。

SK海力士于今年10月宣布,已成功开发出采用1z-nm 制程工艺的DDR4 DRAM,该DDR4 DRAM在单个芯片上实现16Gb,并将于2020年开始规模量产。

SK海力士表示,与上一代制程工艺产品(1y-nm)相比,1z-nm产品将使DRAM生产率提高约27%。另外,为了最大化电容并改善电容器的稳定性,该公司采用了先前工艺中未使用的新材料,并且未使用昂贵的EUV曝光系统,还称具有成本竞争力。

据悉,该1z-nm制程DRAM的数据传输速度达3200Mbps,与采用1y-nm制程的8Gb DRAM芯片组成的相同容量模块相比,它提高了电源效率,降低了约40%的功耗。

该公司还透露,计划将1z-nm制程工艺应用于各种应用,例如下一代移动DRAM LPDDR5和高性能DRAM HBM3。

SK海力士此次宣布的最大关注点是:至少在1z-nm工艺中不会引入EUV。据熟悉韩国半导体行业的人士称,该公司已在其利川总部安装了至少两台用于研究和开发的EUV曝光设备,目前正在同一地点进行建设,并将于2020年下半年完成。EUV有望在2021年全面引入到DRAM生产中,因为M16厂的厂房预计将专门用于DRAM EUV工艺。另外,有传言说,ASML已经为其定制了EUV曝光系统。

另外,竞争对手三星已经为逻辑电路和代工厂引入了EUV,据说华城在建的EUV厂房将在2020年全面投入使用。三星也正在考虑将EUV全面引入DRAM生产中,但尚未透露具体计划。ASML计划在2020年总共交付35个EUV曝光系统,并承认其中一些旨在大规模生产DRAM。但是,目前只有三星,SK海力士和美光这三家主要的DRAM公司,预计每家公司迟早会在1α-nm代制程全面使用EUV。

下图给出了对2020年三星、SK海力和美光的预测。美光将从1x-nm(2019年为70%,2020年43%),1y-nm(15%至27%)和1z-nm(6%至28%),过渡到更先进的1α-nm制程(2020年有望实现2%占比)。

目前,行业DRAM三巨头都没有大规模使用EUV,但随着制程工艺的提升,节点的进一步微缩,同时,EUV的性能和成本也在不断优化,DRAM将迎来EUV爆发期。

DRAM制造商采用EUV的可能性极有可能与逻辑芯片制造商(TSMC,三星代工厂)相似。最初,EUV设备仅用于几层,随着制程节点、层数逐渐增加,将全面转向EUV设备。ASML估计,在DRAM芯片制造方面,每月每启动100,000个晶圆制造项目,一层就需要1.5到2个EUV系统,因此,DRAM制造商需要考虑根据容量和产能来规划相关设备。

需要注意的是,工厂必须为EUV设备做好准备,因为这些步进扫描系统在物理上比DUV设备要大。这就是为什么SK海力士将在京畿道利川市附近建造一个独立的晶圆厂(称为M16),就是要为EUV做好准备。我们不知道美光的新洁净室是否可以用于下一代光刻设备?拭目以待吧。

下载格隆汇APP

下载格隆汇APP

下载诊股宝App

下载诊股宝App

下载汇路演APP

下载汇路演APP

社区

社区

会员

会员